I2C インターフェイス のロジックサンプルを紹介する。

ここで紹介するのは、実際に通信を行う下層レベルのロジック。

温度センサーなどの具体的な通信手順については、「5. I2C ロジックサンプル (応用、温度センサーTMP102 疑似ロジック制御)」」

を参照のこと。

1. 主な仕様

・I2Cクロック周波数 : 100KHz ( at FPGA 20MHz)

・bit順 : MSBファースト (bit7,bit6,bit5...)

・ロジックは、マスター用/スレーブ用に分かれている

・アドレスに続く連続データ数は、最大4バイトまで対応

・アービトレーションには対応していない

・Clock Stretch は (仮)対応中

2. 使い方

・マスター側:

1. 送信BUSY(I2C_CYCLE_BUSY)が解除されるまで待つ

2. 送信先のデバイスアドレス、R/Wビット、全体の送受信データ数(アドレス分も含む)、各バイトの送信データ、

を設定する。

3. MASTER_ACK_MASK は通常動作では'0'に設定する。'1'はエラーテスト用

4. I2C_CYCLE_START='1' で通信開始。(1-CLOCK)

5. 通信終了(SEND_END='1')を待つ。(1-CLOCK)

6. SLAVE_ACK_ERR が '0' であることを確認する。'1' ならエラー発生。

※SLAVE_ACK_ERR は次の通信開始で自動クリアされる。

※途中でエラーが発生しても、マスター側は指定したデータ数分の送受信を最後まで行う。

7. 必要に応じで受信データを取得する。

・スレーブ側:

1. デバイスアドレス、必要に応じで各送信データを設定する。

2. I2Cマスター側から通信を開始する。

3. RECIEVE_END が '1' になるのを待つ。(1-CLOCK)

4. アドレスが一致していること(ADDRESS_MATCH='1')を確認する。

5. MASTER からの ACK応答エラー(MASTER_ACK_ERR)が無いことを確認する。'1'でエラー。

※MASTER_ACK_ERR は次の通信開始で自動クリアされる。

※途中でエラーが発生した場合、SLAVE側は通信を終了する。

6. 必要に応じで受信データを取得する。

※補足:

・MASTER_ACK_MASK は、エラー処理確認用の機能。

'1' に設定すると MASTER がACKを送信しないため、スレーブ側のエラー処理テストが行える。

・手順の詳細については、テストベンチを参照のこと。

3. 設計のポイント

・I2C規格の詳細については以下の資料を参照のこと。※本家NXPサイト(日本語)

https://www.nxp.com/docs/ja/user-guide/UM10204.pdf

・I2Cは、通信自体は単なるシリアルインターフェイスだが、R/Wビット、ACKビットなど、

ビット毎の細かい入出力切替え制御が必要になる。

このサンプルでは、ソースリストの400行目あたり「特殊ビットタイミング」にて、

通信スタート、R/Wビット、MASTER-ACK、SLAVE-ACK、通信ストップ

の各タイミング信号を生成し、これらを組み合わせて SDA の入出力切替えを行っている。

![[picture:pic_ic_fig3]](pic_ic_fig3.png)

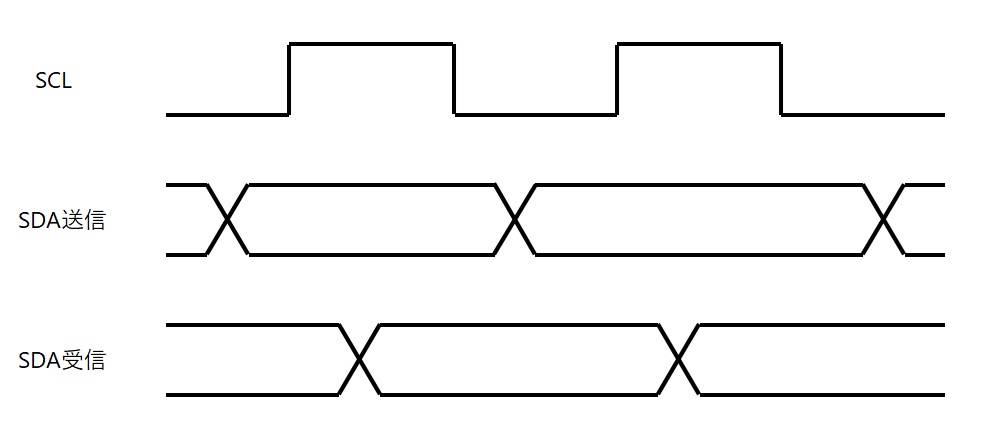

・クロックとデータのタイミング

基本は、

・送信側:クロックの立下り後に送信データを更新

・受信側:クロックの立上り後に受信データを取り込み

タイミングに余裕を持たせるためには、波形変化の直後よりも少し遅らせた方が良い。

本サンプルでは、ノイズカットとディレイを兼ね、スレーブ側の I2C_SCL入力に 1uS のノイズカットを入れている。

なお、実機ではプルアップの関係で波形がなまっていることが多いので注意。

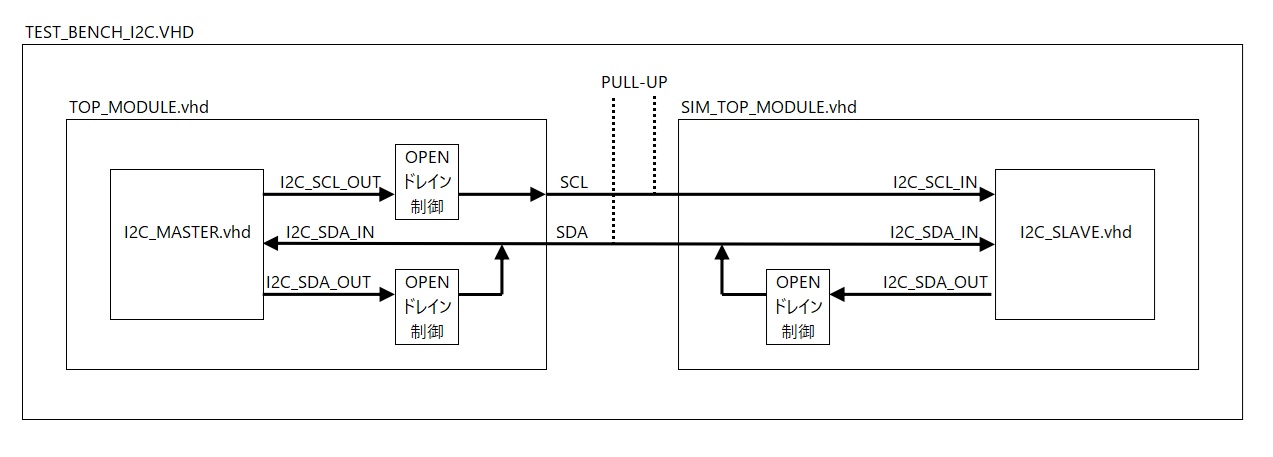

・I2CバスはOPENドレイン出力のため、基板回路上でプルアップ抵抗が付く。

これをシミュレーションするため、

・入力ピンには '1' と 'H' 共に'1'と認識できる記述を入れる

・出力ピンには、OPENドレイン制御の記述を入れる

・テストベンチに PULL-UP の記述を入れる

※補足:以下の理由により、実機にてFPGA内蔵のプルアップ抵抗は使用しないことを勧める。

・抵抗値の誤差が多い

・基板回路図を見ただけでは PULL-UP の有無が確認できない ※図面検査に手間が掛かる

・上記 OPENドレイン制御は、I2Cモジュールではなく各TOPファイルに記述している。

このサンプルでは、I2Cマスター/I2Cスレーブ共に、I2Cモジュールと TOPモジュールとの2階層構造としている。

4. テストベンチについて

テストベンチの構成は上図の通り。

マスターとスレーブを接続して通信させ、if 文で期待値チェックを行う。

詳細は、下記ZIPファイル内 [TEST_BENCH_I2C.VHD]参照のこと。

テストベンチは MODELSIM/VIVADOシミュレーション共通で使える記述にしている。

5. サンプルファイル

プロジェクトファイル一式

・MODELSIM用プロジェクトファイル:japanlogicdesign_i2c_test_modelsim.zip

※MODELSIM プロジェクトは相対パスではないため、ソースファイルの再登録が必要な場合あり。

6. 注意点など

・実機では、必ず波形を確認すること。プルアップ抵抗が大きすぎ、波形がなまり通信エラーを起こすトラブルが多い。

・I2CのバスにバッファICが入っている場合は、そのディレイを配慮してデータ取り込みタイミングを遅らせる必要がある。

・UART等と異なり、I2Cにはパリティビットなどのエラー検出機能が無い。

このため、静電気試験などでノイズを加えた際、データ化けを起こし装置が停止する場合がある。

例:温度センサーにて、静電気放電 -> I2Cバスにノイズ混入 -> 温度データ化け(異常高温) -> 異常温度検出で装置が停止

これを防ぐには、

・オリジナルロジックなら、データーフォーマットにパリティを追加する。

・市販デバイス使用時は、数回分の通信データーが一致した場合のみデータを有効とする。

など、上位プロトコルでのノイズ対策が必要になる。

中国プロテクト:天安門事件、法輪功、チベット

|